|

|

|

|

РОССИЙСКАЯ ФЕДЕРАЦИЯ

ФЕДЕРАЛЬНАЯ СЛУЖБА

ПО ИНТЕЛЛЕКТУАЛЬНОЙ СОБСТВЕННОСТИ,

ПАТЕНТАМ И ТОВАРНЫМ ЗНАКАМ |

(19) |

RU |

(11) |

2381545 |

(13) |

C2 |

|

| (51) МПК

G06F7/50 (2006.01)

|

(12) ОПИСАНИЕ ИЗОБРЕТЕНИЯ К ПАТЕНТУ

| Статус: по данным на 17.09.2010 – действует |

|

|

|

|

|

(21), (22) Заявка: 2008116447/09, 29.04.2008

(24) Дата начала отсчета срока действия патента:

29.04.2008

(46) Опубликовано: 10.02.2010

(56) Список документов, цитированных в отчете о

поиске:

УЭЙКЕРЛИ ДЖ. Проектирование цифровых устройств. т.1. – М.: «Постмаркет», 2002, с.508. RU 2069009 С1, 10.11.1996. SU 997032 A1, 15.02.1983. SU 1594523 A1, 23.09.1990. JP 62204332 A, 09.09.1987. JP 63197227 A, 16.08.1988.

Адрес для переписки:

54040, Украина, г. Николаев, Крылова, 54, кв.229, Л.П.Петренко

|

(72) Автор(ы):

Петренко Лев Петрович (UA)

(73) Патентообладатель(и):

Петренко Лев Петрович (UA)

|

(54) ФУНКЦИОНАЛЬНАЯ СТРУКТУРА ПАРАЛЛЕЛЬНОГО СУММАТОРА С ПРЕДВАРИТЕЛЬНО ВВОДИМЫМИ ПЕРЕНОСАМИ (ВАРИАНТЫ)

(57) Реферат:

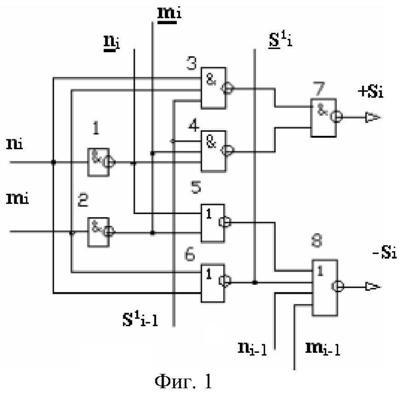

Изобретение относится к вычислительной технике и может быть использовано при построении арифметических устройств и выполнения арифметических операций суммирования частичных произведений в умножителе. Техническим результатом является повышение быстродействия. Каждый разряд устройства в первом варианте реализации содержит два логических элемента НЕ, три логических элемента И-НЕ, три логических элемент ИЛИ-НЕ. 2 н.п. ф-лы, 9 ил.

Текст описания приведен в факсимильном виде.

Формула изобретения

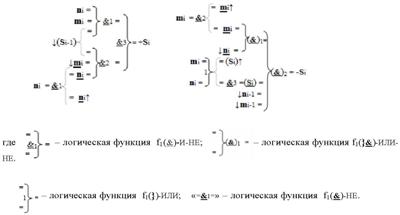

1. Функциональная структура параллельного сумматора с предварительно вводимыми переносами, в которой условно «i» разряд включает логическую функцию f1(})-ИЛИ, в которой две функциональные входные связи являются функциональными входными связями разряда для приема аргументов слагаемых ni и mi, а функциональная выходная связь является выходной функциональной связью разряда для формирования аргумента первой промежуточной суммы S1 i и включает логическую функцию f1(&)-HE, отличающаяся тем, что условно «i» разряд структуры параллельного сумматора выполнен в виде положительного и условно отрицательного канала для формирования аргумента положительной суммы +Si и аргумента условно отрицательной суммы -Si, при этом в положительный канал введены логические функции f1(&)-И-HE, f2(&)-И-НЕ и f3(&)-И-НЕ, а в условно отрицательный канал введены логические функции f2(&)-HE, f1(}&)-ИЛИ-НЕ и f2(}&)-ИЛИ-HE, при этом функциональные связи логических функций в структуре сумматора выполнены в соответствии с математической моделью вида i и включает логическую функцию f1(&)-HE, отличающаяся тем, что условно «i» разряд структуры параллельного сумматора выполнен в виде положительного и условно отрицательного канала для формирования аргумента положительной суммы +Si и аргумента условно отрицательной суммы -Si, при этом в положительный канал введены логические функции f1(&)-И-HE, f2(&)-И-НЕ и f3(&)-И-НЕ, а в условно отрицательный канал введены логические функции f2(&)-HE, f1(}&)-ИЛИ-НЕ и f2(}&)-ИЛИ-HE, при этом функциональные связи логических функций в структуре сумматора выполнены в соответствии с математической моделью вида

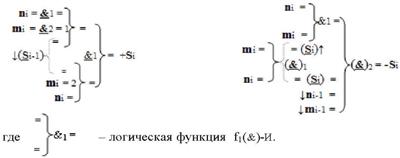

2. Функциональная структура параллельного сумматора с предварительно вводимыми переносами, в которой условно «i» разряд включает логическую функцию f2(})-ИЛИ, в которой две функциональные входные связи являются функциональными входными связями разряда для приема аргументов слагаемых ni и mi, и включает логические функции fi(&)-HE и f1(&)-И, отличающаяся тем, что условно «i» разряд структуры параллельного сумматора выполнен в виде положительного и условно отрицательного канала для формирования аргумента положительной суммы +Si и аргумента условно отрицательной суммы -Si, при этом в положительный канал введены логические функции f2(&)-HE, f1(})-ИЛИ и f1(&)-И-HE, а в условно отрицательный канал введены логические функции f1(}&)-ИЛИ-НЕ и f2(}&)-ИЛИ-НЕ, при этом функциональные связи логических функций в структуре сумматора выполнены в соответствии с математической моделью вида

РИСУНКИ

|

|

|

|

|