|

|

|

|

РОССИЙСКАЯ ФЕДЕРАЦИЯ

ФЕДЕРАЛЬНАЯ СЛУЖБА

ПО ИНТЕЛЛЕКТУАЛЬНОЙ СОБСТВЕННОСТИ,

ПАТЕНТАМ И ТОВАРНЫМ ЗНАКАМ |

(19) |

RU |

(11) |

2378683 |

(13) |

C2 |

|

| (51) МПК

G06F7/50 (2006.01)

|

(12) ОПИСАНИЕ ИЗОБРЕТЕНИЯ К ПАТЕНТУ

| Статус: по данным на 17.09.2010 – действует |

|

|

|

|

|

(21), (22) Заявка: 2006144610/09, 15.12.2006

(24) Дата начала отсчета срока действия патента:

15.12.2006

(43) Дата публикации заявки: 20.06.2008

(46) Опубликовано: 10.01.2010

(56) Список документов, цитированных в отчете о

поиске:

Дж.УЭЙКЕРЛИ Проектирование цифровых устройств. T.1 – М.: Постмаркет, 2002, с.508. RU 2069009 C1, 10.11.1996. SU 997032 A1, 15.02.1983. SU 1594523 A1, 23.09.1990. JP 62204332 A, 09.09.1987. JP 63197227 A, 16.08.1988.

Адрес для переписки:

54040, Украина, г. Николаев, Крылова, 54, кв.229, Л.П. Петренко

|

(72) Автор(ы):

Петренко Лев Петрович (UA)

(73) Патентообладатель(и):

Петренко Лев Петрович (UA)

|

(54) СПОСОБ ПАРАЛЛЕЛЬНОГО ЛОГИЧЕСКОГО СУММИРОВАНИЯ ПОСЛЕДОВАТЕЛЬНОСТЕЙ АНАЛОГОВЫХ СИГНАЛОВ СЛАГАЕМЫХ ЭКВИВАЛЕНТНЫХ ДВОИЧНОЙ СИСТЕМЕ СЧИСЛЕНИЯ

(57) Реферат:

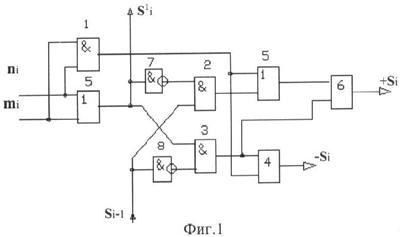

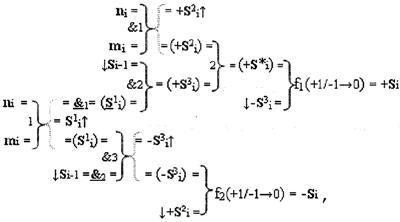

Изобретение относится к вычислительной технике и может быть использовано при построении арифметических устройств для выполнения арифметических операций в позиционно-знаковых кодах. Техническим результатом является повышение быстродействия. Способ заключается в следующем: из входных аналоговых сигналов ni и mi в «i» разряде формируют аналоговые сигналы первой промежуточной логической суммы S1 i, посредством логических функций ИЛИ1 и второй промежуточной логической суммы S2 i, посредством логических функций ИЛИ1 и второй промежуточной логической суммы S2 i, посредством логических функций И1, формируют положительный производный аналоговый сигнал +S3 i, посредством логических функций И1, формируют положительный производный аналоговый сигнал +S3 i посредством логической функции И2 из предварительно измененного функцией НЕ1 по уровню аналогового сигнала S1 i посредством логической функции И2 из предварительно измененного функцией НЕ1 по уровню аналогового сигнала S1 i и первой промежуточной суммы S1 i и первой промежуточной суммы S1 i-1 «i-1» разряда, а условно отрицательный производный аналоговый сигнал -S3 i-1 «i-1» разряда, а условно отрицательный производный аналоговый сигнал -S3 i формируют посредством логической функции И3 из аналогового сигнала S1 i формируют посредством логической функции И3 из аналогового сигнала S1 i и предварительно измененного функцией НЕ2 по уровню аналогового сигнала S1 i и предварительно измененного функцией НЕ2 по уровню аналогового сигнала S1 i-1 первой промежуточной суммы S1 i-1 первой промежуточной суммы S1 i-1 «i-1» разряда, аналоговый сигнал +S3 i-1 «i-1» разряда, аналоговый сигнал +S3 i совмещают с аналоговым сигналом +S2 i совмещают с аналоговым сигналом +S2 i посредством логической функции ИЛИ2 и выполняют изменение уровня аналогового сигнала результирующего аргумента +S*i, что соответствует процедуре удаления активного логического нуля, который формируется, если совмещенный аналоговый сигнал +S*i и условно отрицательный производный аналоговые сигналы -S3 i посредством логической функции ИЛИ2 и выполняют изменение уровня аналогового сигнала результирующего аргумента +S*i, что соответствует процедуре удаления активного логического нуля, который формируется, если совмещенный аналоговый сигнал +S*i и условно отрицательный производный аналоговые сигналы -S3 i принимают одновременно активные уровни аналогового сигнала, выполняют удаление активного уровня аналогового сигнала при совпадении условно отрицательного производного аналогового сигнала -S3 i принимают одновременно активные уровни аналогового сигнала, выполняют удаление активного уровня аналогового сигнала при совпадении условно отрицательного производного аналогового сигнала -S3 i с аналоговым сигналом второй промежуточный суммы +S2 i с аналоговым сигналом второй промежуточный суммы +S2 i. 5 ил. i. 5 ил.

Текст описания приведен в факсимильном виде.

Формула изобретения

Способ параллельного логического суммирования аналоговых сигналов слагаемых эквивалентных двоичной системе счисления, включающий поразрядное выполнение преобразований аналоговых сигналов слагаемых [ni] и [mi], которые принимают либо условно высокий или активный уровень, либо условно низкий сигнал или неактивный уровень, при этом из входных аналоговых сигналов ni и mi в «i» разряде формируют аналоговые сигналы первой промежуточной логической суммы S1 i, посредством логических функций f1(})-ИЛИ и второй промежуточной логической суммы S2 i, посредством логических функций f1(})-ИЛИ и второй промежуточной логической суммы S2 i, посредством логических функций f1(&)-И, из которых формируют аналоговый сигнал Si результата логического суммирования, отличающийся тем, что аналоговый сигнал первой промежуточной логической суммы S1 i, посредством логических функций f1(&)-И, из которых формируют аналоговый сигнал Si результата логического суммирования, отличающийся тем, что аналоговый сигнал первой промежуточной логической суммы S1 i логически дифференцируют с одновременным формированием производных аналоговых сигналов положительного +S3 i логически дифференцируют с одновременным формированием производных аналоговых сигналов положительного +S3 i и условно отрицательного -S3 i и условно отрицательного -S3 i, при этом положительный производный аналоговый сигнал +S3 i, при этом положительный производный аналоговый сигнал +S3 i формируют посредством логической функции f2(&)-И из предварительно измененного функцией f1(&)-HE по уровню аналогового сигнала S1 i формируют посредством логической функции f2(&)-И из предварительно измененного функцией f1(&)-HE по уровню аналогового сигнала S1 i первой промежуточной суммы S1 i первой промежуточной суммы S1 i «i» разряда и первой промежуточной суммы S1 i «i» разряда и первой промежуточной суммы S1 i-1 «i-1» разряда, а условно отрицательный производный аналоговый сигнал -S3 i-1 «i-1» разряда, а условно отрицательный производный аналоговый сигнал -S3 i формируют посредством логической функции f3(&)-И из аналогового сигнала первой промежуточной суммы S1 i формируют посредством логической функции f3(&)-И из аналогового сигнала первой промежуточной суммы S1 i «i» разряда и предварительно измененного функцией f2(&)-HE по уровню аналогового сигнала S1 i «i» разряда и предварительно измененного функцией f2(&)-HE по уровню аналогового сигнала S1 i-1 первой промежуточной суммы S1 i-1 первой промежуточной суммы S1 i-1 «i-1» разряда, после чего в «i» разряде положительный производный аналоговый сигнал +S1 i-1 «i-1» разряда, после чего в «i» разряде положительный производный аналоговый сигнал +S1 i совмещают с аналоговым сигналом второй промежуточной суммы +S2 i совмещают с аналоговым сигналом второй промежуточной суммы +S2 i посредством логической функции f2(})-ИЛИ и выполняют изменение уровня аналогового сигнала результирующего аргумента +S*i, что соответствует процедуре удаления активного логического нуля f1(+1/-1 i посредством логической функции f2(})-ИЛИ и выполняют изменение уровня аналогового сигнала результирующего аргумента +S*i, что соответствует процедуре удаления активного логического нуля f1(+1/-1 0), которые формируется, если совмещенный аналоговый сигнал +S*i и условно отрицательный производный аналоговые сигналы -S3 0), которые формируется, если совмещенный аналоговый сигнал +S*i и условно отрицательный производный аналоговые сигналы -S3 i принимают одновременно активные уровни аналогового сигнала, при этом выполняют изменение (удаление) активного уровня аналогового сигнала f2(+1/-1 i принимают одновременно активные уровни аналогового сигнала, при этом выполняют изменение (удаление) активного уровня аналогового сигнала f2(+1/-1 0) при совпадении условно отрицательного производного аналогового сигнала S3 0) при совпадении условно отрицательного производного аналогового сигнала S3 i с аналоговым сигналом второй промежуточной i с аналоговым сигналом второй промежуточной

суммы +S2 i в соответствии с математической моделью вида i в соответствии с математической моделью вида

где

логические функции f1(&)-И и f1(})-ИЛИ;

функциональная структура удаления активного логического нуля при одновременно активных аналоговых сигналов;

«=&1=» – логическая функция изменения уровня аналогового сигнала f1(&)-НЕ.

РИСУНКИ

|

|

|

|

|