|

|

(21), (22) Заявка: 2003133457/09, 17.04.2002

(24) Дата начала отсчета срока действия патента:

17.04.2002

(30) Конвенционный приоритет:

18.04.2001 (пп.1-28) US 60/284,791

(43) Дата публикации заявки: 10.05.2005

(46) Опубликовано: 10.09.2007

(56) Список документов, цитированных в отчете о

поиске:

US 6043714 А, 28.03.2000. SU 754646, 10.08.1980. US 5808511 А, 15.09.1988. US 6137366 А, 24.10.2000.

(85) Дата перевода заявки PCT на национальную фазу:

18.11.2003

(86) Заявка PCT:

US 02/12190 (17.04.2002)

(87) Публикация PCT:

WO 02/087072 (21.10.2002)

Адрес для переписки:

129010, Москва, ул. Б. Спасская, 25, стр.3, ООО “Юридическая фирма Городисский и Партнеры”, пат.пов. Ю.Д.Кузнецову, рег.№ 595

|

(72) Автор(ы):

АПАРИН Владимир (US)

(73) Патентообладатель(и):

КВЭЛКОММ ИНКОРПОРЕЙТЕД (US)

|

(54) СПОСОБ И СХЕМА СМЕЩЕНИЯ ДЛЯ СНИЖЕНИЯ ИСКАЖЕНИЙ

(57) Реферат:

Изобретение относится к электронной технике. Технический результат заключается в устранении компонент нежелательных искажений. Предложенная схема смещения генерирует оптимальное напряжение смещения для транзистора, при котором его выбранная нелинейность равна нулю. Математически нелинейность может быть представлена суммой множества компонент, причем некоторые компоненты имеют отрицательный знак. Компоненты пропорциональны постоянным токам (ПТ) транзистора при напряжениях смещения, отличающихся на незначительную величину. Схема смещения включает в себя транзисторы смещения, которые являются масштабированными версиями главного транзистора. Каждый транзистор смещения генерирует ПТ, представляющий одну из компонент. Предложен способ смещения, согласно которому токи объединяют в соответствии со знаками соответствующих компонент для формирования сигнала ПТ, пропорционального выбранной нелинейности. Схема обратной связи считывает сигнал ПТ и генерирует напряжения смещения транзисторов смещения, которые заставляют сигнал ПТ быть равным нулю. Одно из напряжений смещения подают на главный транзистор, что в результате приводит к устранению его выбранной нелинейности. 3 н. и 25 з.п. ф-лы, 5 ил.

Область техники, к которой относится изобретение

Настоящее изобретение относится в общем к транзисторным схемам и более конкретно к способу и схеме смещения для снижения искажений.

Уровень техники

Транзисторные усилители и смесители являются широко используемыми структурными блоками аналоговых схем, работающих в диапазоне от звуковых частот (ЗЧ) до радиочастот (РЧ). В общем эти схемы требуются для минимизации искажения сигнала и предназначены для сохранения информации, переносимой сигналом.

Искажение сигнала в активных схемах имеет место из-за нелинейностей транзистора. Рассмотрим простой усилитель с общим истоком МОП-структуры с каналом n-типа, а также его эквивалентную схему, показанные на Фиг.1А и 1В соответственно. На Фиг.1А М1 является МОП-транзистором с каналом n-типа, С является разделительным конденсатором постоянного тока (ПТ), RL является резистором смещения в цепи стока. Эквивалентная схема по Фиг.1В является идеальной моделью схемы по Фиг.1А. На Фиг. 1В VGS является напряжением затвор-исток, а ID является током стока М1. Ток стока ID является функцией VGS. Для соответствующей работы затвор транзистора М1 должен иметь смещение выше порогового напряжения, чтобы обеспечить возможность протекания через М1 не равного нулю постоянного тока (ПТ) стока. Напряжение смещения в цепи затвора генерируется дополнительными схемами, которые в общем показаны на Фиг. 1А и 1В как схема смещения.

Общепринятая известная схема смещения показана на Фиг.2, где транзистор М2 представляет собой масштабированную версию (копию) транзистора М1 с той же самой длиной затвора, но более узкой шириной. На Фиг.2 также показаны опорный источник тока IREF и резистор RB смещения, который изолирует цепь смещения от входа усилителя на рабочей частоте усилителя. Сток транзистора М1 смещен в области насыщения для высокого усиления. В идеальном случае транзистор М1 работает как линейный источник тока, управляемый напряжением, имеющий следующие характеристики:

где VTH является пороговым напряжением транзистора М1 и gm является независящим от смещения коэффициентом, называемым крутизной (активной междуэлектродной проводимостью) в единицах ампер/вольт (А/В).

Для дальнейшего анализа будет удобным разделить величины постоянного тока ID и VGS от их величин перемененного тока, используя следующие соотношения:

где ID0 является постоянным током стока и VGS0 является напряжением постоянного тока затвор-исток транзистора М1, генерированным схемой смещения. В уравнении (2) vGS является напряжением переменного тока затвор-исток, равным напряжению входного сигнала (vIN) и iD является переменным током стока. Уравнение (1) может быть записано в значениях введенных величин переменного тока следующим образом:

где все члены были предварительно определены.

Когда подают к схеме входной сигнал переменного тока vIN, транзистор М1 генерирует выходной переменный ток, равный gmvIN, который создает падение напряжения на резисторе RL смещения в цепи стока, равное -gmvINRL. Это напряжение на резисторе RL смещения в цепи стока является выходным сигналом усилителя, а -gmRL является его усилением.

В идеальном усилителе, показанном на Фиг.1А и 1В, выходной сигнал является масштабированной версией входного сигнала (то есть отсутствуют паразитные выходные сигналы системы). Спектр выходного сигнала имеет те же самые частотные компоненты (составляющие), что и входной сигнал.

К сожалению, активная междуэлектродная проводимость реального транзистора не является константой, а представляет собой функцию выходного напряжения смещения. Эту функцию часто описывают сложным уравнением или системой уравнений. Для упрощения схемного анализа эту функцию заменяют ее разложением в ряд Тейлора вблизи VGS0 следующим образом:

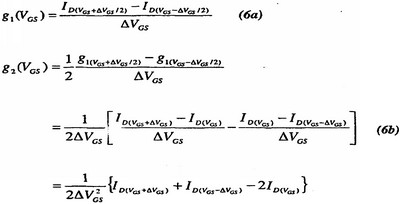

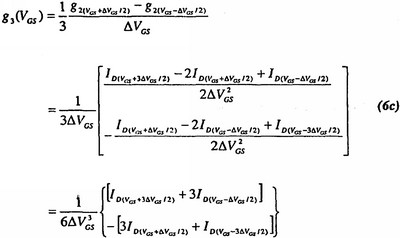

где g1, g2 и g3 являются коэффициентами разложения, равными:

Подставляя это разложение gm в уравнение (3), мы получим следующее выражение для выходного тока для реального МОП-транзистора с каналом n-типа:

Это разложение часто называют степенным рядом. Первый член в этом ряде называют линейным членом, и он представляет требуемую функцию транзистора (например, транзистора М1). Второй член называют нелинейностью 2-го порядка. Третий член называют нелинейностью 3-го порядка и т.д. Нелинейности нежелательны, так как они генерируют паразитные выходные сигналы, которые создают помехи требуемому сигналу.

Известны несколько широко распространенных методов для снижения паразитных выходных сигналов схемы относительно их требуемых основных выходных сигналов. Эти методы часто называют методами линеаризации. Самый простой и широко используемый метод основан на том факте, что коэффициенты разложения 2-го и 3-го порядка выходного тока полевого транзистора, g2 и g3, снижаются относительно линейной активной междуэлектродной проводимости g1 при напряжениях затвор-сток гораздо больших, чем пороговое напряжение. Таким образом, выбирая достаточно большое VGS0, можно в результате получить гораздо меньшие паразитные выходные сигналы относительно основного выходного сигнала схемы. К сожалению, этот метод увеличивает потребление постоянного тока схемы, которое может оказаться неприемлемым для некоторых применений (например, для работающих на батареях устройств).

Другой метод основан на том факте, что для многих полевых транзисторов имеют место определенные входные напряжения смещения, при которых или коэффициент разложения 2-го порядка, или коэффициент разложения 3-го порядка равны нулю. Эти напряжения смещения, как правило, близки к пороговому напряжению, и поэтому не приводят к большому постоянному току стока. Если транзистор имеет смещение при таком напряжении, теоретически он генерирует нулевое искажение 2-го или 3-го порядка. Имеется возможность вычислить напряжение смещения, при котором g2 или g3 равны нулю, из смоделированной или измеренной передаточной характеристики транзистора. Вычисленное напряжение смещения будет оптимальным только для типового транзистора, для которого была выведена модель, или для измеренного транзистора-образца. Оно также будет оптимальным лишь при определенной температуре, при которой передаточная характеристика была смоделирована или измерена. Имеется возможность спроектировать схему смещения, которая генерирует это вычисленное напряжение затвор-исток, при котором g2 или g3 равны нулю, используя, например, резистивный делитель. Однако она не будет удовлетворительно устранять соответствующее искажение, когда изменяется рабочая температура или имеют место отклонения параметров в процессе производства транзисторов.

Следовательно, будет понятным, что имеет место существенная потребность в схеме смещения для устранения компонент (составляющих) нежелательных искажений независимо от температурных флуктуаций и отклонений в процессе производства транзисторов.

Настоящее изобретение обеспечивает это преимущество, а также другие преимущества, как это станет очевидным из нижеприведенного подробного описания и сопроводительных чертежей.

Сущность изобретения

Настоящее изобретение осуществлено в способе и схеме смещения транзистора. Транзистор, который должен быть смещен, имеет передаточную характеристику, которая может отличаться линейным членом или членом первого порядка, описывающим прямую линию, и нелинейными членами или членами более высокого порядка, такими как нелинейности 2-го и 3-го порядка, которые описывают отклонения передаточной характеристики от прямой линии. Согласно способу изобретения генерируют сигнал постоянного тока, пропорциональный выбранной нелинейности транзистора, и используют сигнал постоянного тока для генерирования напряжения смещения транзистора, при котором выбранная нелинейность является нулевой.

В одном примере выбранная нелинейность является нелинейностью 2-го порядка, и сигнал постоянного тока включает в себя первую, вторую и третью части. Первая, вторая и третья части объединяются для формирования сигнала постоянного тока. В другом примере выбранная нелинейность является нелинейностью 3-го порядка, и сигнал постоянного тока включает в себя первую, вторую, третью и четвертую части. Первая, вторая, третья и четвертая части объединяются для формирования сигнала постоянного тока.

Согласно способу также предусматривают зеркало для элементов схемы смещения, генерирующих сигнал постоянного тока. Цепь обратной связи может быть также предусмотрена для считывания сигнала постоянного тока и генерирования напряжения смещения, при котором сигнал постоянного тока и выбранная нелинейность равны нулю. Сигнал постоянного тока может быть током или напряжением, односторонним или дифференциальным.

Выходной сигнал транзистора может отличаться степенным рядом, имеющим линейный член и нелинейные члены или нелинейности. Каждая из нелинейностей состоит из множества компонент. Схема смещения может включать в себя отдельные транзисторы смещения, предназначенные для генерирования частей сигнала постоянного тока, соответствующих отдельным компонентам выбранной нелинейности. Части сигнала постоянного тока объединяются для формирования сигнала постоянного тока, пропорционального выбранной нелинейности. Цепь обратной связи может быть предусмотрена для считывания сигнала постоянного тока и генерирования напряжений смещения транзисторов смещения, при которых сигнал постоянного тока и выбранная нелинейность равны нулю. Например, нелинейность 2-го порядка может отличаться первой, второй и третьей компонентами. Схема смещения может включать в себя первый, второй и третий транзисторы смещения, которые генерируют части сигнала постоянного тока, соответствующие первой, второй и третьей компонентам. Части сигнала постоянного тока объединяются для формирования сигнала постоянного тока, пропорционального нелинейности 2-го порядка. Схема обратной связи считывает сигнал постоянного тока и генерирует напряжения смещения транзисторов смещения, при которых сигнал постоянного тока равен нулю. Одно из этих напряжений подается на главный транзистор, эффективно подавляя нелинейность 2-го порядка.

Краткое описание чертежей

Фиг.1А – обычный усилитель на транзисторе с общим истоком.

Фиг.1В – эквивалентная схема усилителя с общим истоком по Фиг.1А

Фиг.2 – обычная схема смещения, используемая для смещения усилителя на транзисторе с общим истоком по Фиг.1А.

Фиг. 3А-3D – ряд графиков, иллюстрирующих передаточную характеристику типового транзистора и ее коэффициенты разложения степенного ряда как функции входного напряжения смещения.

Фиг.4 – приведенный в качестве примера вариант схемы осуществления смещения настоящего изобретения, предназначенной для генерирования входного напряжения смещения, в котором нелинейность 2-го порядка равна нулю.

Фиг.5 – альтернативный вариант осуществления схемы смещения настоящего изобретения, предназначенной для генерирования входного напряжения смещения, в котором нелинейность 3-го порядка равна нулю.

Подробное описание предпочтительных вариантов осуществления

Настоящее изобретение описывает способ и схему смещения для селективного снижения нелинейностей 2-го и 3-го порядка транзистора и соответствующих искажений сигнала. Описанные здесь методы реализуются удовлетворительно несмотря на отклонения производственного процесса от одной схемы к другой и температурные флуктуации.

Принципы настоящего изобретения основаны на том факте, что для многих транзисторов коэффициенты разложения 2-го и 3-го порядка выходного тока (например, g2 и g3) зависят от входного напряжения смещения. То есть переменный выходной ток iD уравнения (5) представляет собой степенной ряд, включающий нелинейности 2-го и 3-го порядка, характеризующиеся коэффициентами разложения 2-го и 3-го порядка, g2 и g3 соответственно. В свою очередь значения коэффициентов разложения g2 и g3 зависят от входного напряжения смещения. Эта зависимость является такой, что при конкретном входном напряжении смещения или g2, или g3 равно нулю. Если вход усилителя имеет смещение при этом напряжении, нелинейность 2-го или 3-го порядка будет подавлена и сигнал не будет иметь искажения 2-го или 3-го порядка.

В качестве примера рассмотрим схему транзистора по Фиг.1А и ее эквивалентную схему, показанную на Фиг.1В. Как уже ранее указывалось, ток стока ID является функцией напряжения затвор-сток VGS. Передаточная характеристика МОП-транзистора с коротким каналом n-типа показана на Фиг.3А, где ток стока ID отложен на графике как функция напряжения затвор-сток VGS. Фиг.3В-3D являются графиками коэффициентов разложения g1-g3, полученных из уравнения (4b). Фиг.3В иллюстрирует линейную активную междуэлектродную проводимость транзистора М1. Фиг.3С иллюстрирует коэффициент нелинейности 2-го порядка. Следует отметить, что коэффициент разложения g2 и соответствующее искажение 2-го порядка равны нулю при VGS=1,63В. Фиг.3D иллюстрирует коэффициент нелинейности 3-го порядка транзистора М1. Следует отметить, что коэффициент разложения g3 и соответствующее искажение 3-го порядка равны нулю при VGS=0,74В.

Используя методы известного уровня техники, возможно использование обычного резистивного делителя для смещения транзистора М1 фиксированным напряжением постоянного тока. Например, Фиг.3D иллюстрирует, что напряжение смещения, приблизительно равное 0,74В, приводит в результате к нулевому значению коэффициента разложения g3. Однако следует понять, что характеристические кривые по Фиг.3А-3D представляют единственный МОП-транзистор с каналом n-типа при определенной температуре. Температурные флуктуации и отклонения в производственном процессе изготовления транзистора обусловливают сдвиг этих характеристик относительно оси VGS. Ступенчатый уклон характеристики g3 на Фиг.3D у нулевой точки пересечения иллюстрирует, что даже незначительные сдвиги в этой точке будут значительно увеличивать искажение 3-го порядка, если напряжение смещения остается фиксированным при 0,74В. Следовательно, схемы фиксированного напряжения смещения постоянного тока, известные из уровня техники, недостаточны для достижения стабильного снижения или устранения искажения 2-го или 3-го порядка. Требуется спроектировать схему смещения, которая автоматически генерирует и сохраняет оптимальное напряжение смещения, которое подавляет выбранную нелинейность при флуктуирующей температуре и отклоняющихся производственных условиях. Настоящее изобретение направлено на удовлетворение этого требования.

Для генерирования и сохранения оптимального напряжения смещения, приводящего к нулевому искажению 2-го или 3-го порядка, схема смещения должна иметь дубликат усиливающего транзистора, такого как транзистор смещения М2 по Фиг.2, и средство для создания измеряемой электрической величины, такой как напряжение постоянного тока или ток, пропорциональный g2 или g3 транзистора-дубликата. Также потребуется обратная связь постоянного тока, которая считывает эту величину и автоматически регулирует напряжение смещения как усиливающего транзистора, так и его копии для g2=0 или g3=0.

Можно достичь понимания того, как генерировать напряжение постоянного тока или тока, пропорционального g2 или g3, если уравнения (4b) переписать в значениях малых отклонений напряжений и токов, а не в значениях производных.

Следует заметить, что члены в круглых скобках в уравнениях (6а-6с) указывают на рабочие параметры. Например, член ID(VGS+ VGS) в уравнении (6b) предназначен для указания тока ID при напряжении VGS+ VGS) в уравнении (6b) предназначен для указания тока ID при напряжении VGS+ VGS. Аналогичным образом член ID(VGS+3 VGS. Аналогичным образом член ID(VGS+3 VGS/2) в уравнении (6с) указывает на ток ID при напряжении VGS+3 VGS/2) в уравнении (6с) указывает на ток ID при напряжении VGS+3 VGS/2. Член VGS/2. Член  VGS является малым отклонением от VGS. Члены в фигурных скобках уравнений (6b) и (6c) являются измеряемыми величинами, которые должны быть установлены на ноль для g2=0 или g3=0, чтобы подавить искажение соответственно 2-го порядка или 3-го порядка. Фиг.4 иллюстрирует один пример схемы смещения, которая генерирует член в фигурных скобках уравнения (6b) и автоматически регулирует VGS для установки этого члена на ноль. VGS является малым отклонением от VGS. Члены в фигурных скобках уравнений (6b) и (6c) являются измеряемыми величинами, которые должны быть установлены на ноль для g2=0 или g3=0, чтобы подавить искажение соответственно 2-го порядка или 3-го порядка. Фиг.4 иллюстрирует один пример схемы смещения, которая генерирует член в фигурных скобках уравнения (6b) и автоматически регулирует VGS для установки этого члена на ноль.

Транзисторы М2а, М2b и М2с являются дубликатами транзистора М1 по Фиг.1, имея ту же самую длину затвора, как у транзистора М1, но его ширина изображена в меньшем масштабе. Затворы трех дубликатов имеют смещение через резисторную цепочку 2R, 2R с током I0 стока. Величину R резисторного блока и величину I0 тока стока выбирают так, чтобы падение напряжения I0 R было равно  VGS/2 в уравнениях (6а)-(6с). Величину каждого резистора по Фиг.4 выбирают равной 2R, так чтобы падения напряжения можно было удобно измерить в значениях VGS/2 в уравнениях (6а)-(6с). Величину каждого резистора по Фиг.4 выбирают равной 2R, так чтобы падения напряжения можно было удобно измерить в значениях  VGS. VGS.

Схема на Фиг.4 работает удовлетворительно тогда, когда величина для  VGS гораздо меньше, чем величина для VGS для обеспечения того, чтобы VGS+ VGS гораздо меньше, чем величина для VGS для обеспечения того, чтобы VGS+ VGS и VGS– VGS и VGS– VGS были близки к VGS. Например, если был выбран ток I0, равный 0,05мА, а 2R были выбраны равными 400 Ом, то величина VGS были близки к VGS. Например, если был выбран ток I0, равный 0,05мА, а 2R были выбраны равными 400 Ом, то величина  VGS будет равной 20 мВ. Фактическая величина для VGS будет равной 20 мВ. Фактическая величина для  VGS выбирается при проектировании в пределах знаний схемного проектировщика, используя вышеописанные принципы. Таким образом, настоящее изобретение не ограничивается определенной величиной тока I0, величиной R резисторного блока или выбранной величиной для VGS выбирается при проектировании в пределах знаний схемного проектировщика, используя вышеописанные принципы. Таким образом, настоящее изобретение не ограничивается определенной величиной тока I0, величиной R резисторного блока или выбранной величиной для  VGS. VGS.

Все три транзистора смещения (М2а, М2b и М2с) имеют то же самое соотношение ширина/длина (Ш/Д). Транзисторы М2а и М2с являются устройствами с единственным транзистором, тогда как транзистор М2b состоит из двух параллельных устройств, каждое из которых имеет тот же самый размер, что и транзисторы М2а и М2с. Это показано в схеме на Фиг.4 обозначением m=2, относящимся к транзистору М2b, где m-коэффициент умножения.

Транзистор М2а генерирует ток, представленный первым слагаемым, показанным в фигурных скобках уравнения (6b). То есть транзистор М2а генерирует ток, имеющий величину, равную ID(VGS+ VGS). В противоположность этому транзистор М2с генерирует ток, представленный вторым слагаемым, показанным в фигурных скобках уравнения (6b). То есть транзистор М2с генерирует ток, имеющий величину, которая равна ID(VGS– VGS). В противоположность этому транзистор М2с генерирует ток, представленный вторым слагаемым, показанным в фигурных скобках уравнения (6b). То есть транзистор М2с генерирует ток, имеющий величину, которая равна ID(VGS– VGS). Наконец, транзистор М2b генерирует ток, представленный третьим слагаемым, показанным в фигурных скобках уравнения (6b). То есть транзистор М2b генерирует ток, равный 2ID(VGS). VGS). Наконец, транзистор М2b генерирует ток, представленный третьим слагаемым, показанным в фигурных скобках уравнения (6b). То есть транзистор М2b генерирует ток, равный 2ID(VGS).

Токи транзисторов М2а и М2с суммируются при соединении их стоков вместе. Общий сток транзисторов М2а и М2с и сток транзистора М2b получают смещение через токовое зеркало, включающее в себя пару транзисторов М3а и М3b, где М3а и М3b являются МОП-транзисторами одинакового размера с каналом р-типа. Дифференциальное напряжение постоянного тока между стоками транзисторов М3а и М3b является сигналом постоянного тока, пропорциональным члену математического выражения в фигурных скобках уравнения (6b) и, таким образом, пропорциональным коэффициенту разложения g2. Если дифференциальное напряжение равно нулю, то объединенный ток транзисторов М2а и М2с равен току транзистора М2b и член в фигурных скобках уравнения (6b) будет равен нулю. Транзистор М3b является токовым зеркалом, которое генерирует тот же самый ток, что и транзистор М3а, при условии, что напряжение его стока будет тем же самым, что и напряжение стока транзистора М3а.

Этот баланс токов обеспечивается операционным усилителем ОУ1 на Фиг.4, который считывает дифференциальное напряжение постоянного тока между стоками транзисторов М3а и М3b и генерирует входное напряжение для резисторной цепочки 2R, 2R, создавая, таким образом, петлю обратной связи. Функция операционного усилителя ОУ1 легко понятна для схемного проектировщика, если учитывать приведенную в качестве примера схему по Фиг.4. В общем операционный усилитель ОУ1 усиливает дифференциальное входное напряжение с высоким усилением и подает усиленное напряжение на затворы транзисторов М2а, М2b и М2с с такой полярностью, что рабочая точка этих транзисторов регулируется до тех пор, пока напряжения их стоков не будут равными.

Затвор и сток транзистора М3а соединены вместе. Положительный вход операционного усилителя ОУ1 связан с узлом стоков транзисторов М3b и М2b. Если, например, напряжение стока транзистора М3b увеличивается, выход операционного усилителя ОУ1 обеспечивает возросший сигнал, непосредственно подаваемый на затвор транзистора М2а и на затворы транзисторов М2b и М2с через резисторную цепочку 2R, 2R. Возросшее напряжение затвора транзистора М2b обусловливает снижение напряжения его затвора, таким образом, приводя напряжение затвора транзистора М3b в равновесие с напряжением его затвора, которое является также напряжением на затворе и стоке транзистора М3а. Поэтому токи стока транзисторов М3а и М3b поддерживаются одинаковыми.

Таким образом, напряжение VGS по Фиг.4 является требуемым напряжением смещения, которое будет устранять воздействие нелинейности 2-го порядка (то есть g2=0). Напряжение смещения подается на затвор транзистора М1 (см. Фиг.1а) через транзистор Rb, который предназначен для изоляции схемы смещения от транзистора М1 на рабочей частоте. В приведенном в качестве примера варианте осуществления сопротивление Rb изолирующего транзистора может иметь величину около 10 кОм. Цепь обратной связи на Фиг.4 автоматически поддерживает VGS, подаваемое на затвор М1 по Фиг.1а, на уровне, который обусловливает равенство нулю нелинейности 2-го порядка даже при наличии производственных и температурных отклонений.

Схема на Фиг.4 селективно генерирует токи, пропорциональные компонентам нелинейности 2-го порядка, которые используются для генерирования напряжения смещения для эффективного подавления нелинейности 2-го порядка. Аналогичный подход к решению может быть использован для подавления нелинейности 3-го порядка. Фиг.5 иллюстрирует приведенный в качестве примера вариант осуществления схемы, которая эффективно подавляет член математического выражения в фигурных скобках уравнения (6с), устанавливая, таким образом, величину коэффициента g3 разложения равной нулю.

Хотя схема на Фиг.5 работает аналогичным образом, как и схема на Фиг.4, некоторые дополнительные пояснения могут способствовать лучшему пониманию ее работы. Анализ уравнения (6с) показывает, что имеются четыре слагаемых, содержащихся в фигурных скобках. Каждый из транзисторов М2а, М2b, М2с и М2d на Фиг.5 генерирует постоянный ток, представленный соответствующим слагаемым в фигурных скобках уравнения (6с). Транзисторы М2а, М2b, М2с и М2d являются дубликатами транзистора М1 на Фиг.1, имеющими ту же самую длину затвора, что и транзистор М1, но их ширина изображена в меньшем масштабе. Затворы четырех дубликатов получают смещение при прохождении через резисторную цепочку 2R,R,R,2R тока I0 стока.

Падение напряжения, создаваемое при прохождении тока I0 через сопротивление R, эквивалентно  VGS/2 в уравнениях (6а)-(6с). Это падение напряжения выбирается сравнительно малым, так чтобы VGS +3 VGS/2 в уравнениях (6а)-(6с). Это падение напряжения выбирается сравнительно малым, так чтобы VGS +3 VGS/2 и VGS -3 VGS/2 и VGS -3 VGS/2 были близки VGS. Как обсуждалось выше, единственным требованием является то, чтобы VGS/2 были близки VGS. Как обсуждалось выше, единственным требованием является то, чтобы  VGS было гораздо меньше, чем VGS. Аналогичным образом величины для резисторов R и 2R могут быть выбраны инженером, чтобы получить удобные величины резисторов. Величина I0 тока стока также выбирается проектировщиком на основании приведенного здесь описания. Например, если схема по настоящему изобретению предназначена для использования в питающейся от батареи схеме, будет целесообразным минимизировать потребление тока I0 через сток тока и потребление мощности в резисторах R и 2R для выбранного VGS было гораздо меньше, чем VGS. Аналогичным образом величины для резисторов R и 2R могут быть выбраны инженером, чтобы получить удобные величины резисторов. Величина I0 тока стока также выбирается проектировщиком на основании приведенного здесь описания. Например, если схема по настоящему изобретению предназначена для использования в питающейся от батареи схеме, будет целесообразным минимизировать потребление тока I0 через сток тока и потребление мощности в резисторах R и 2R для выбранного  VGS. В противоположность этому схема, имеющая внешний источник питания, не имеет таких ограничений. Таким образом, настоящее изобретение не ограничено конкретными величинами, выбранными для резисторов R и 2R, или величиной тока I0 через сток тока. VGS. В противоположность этому схема, имеющая внешний источник питания, не имеет таких ограничений. Таким образом, настоящее изобретение не ограничено конкретными величинами, выбранными для резисторов R и 2R, или величиной тока I0 через сток тока.

Все четыре транзистора имеют то же самое соотношение ширина/длина (Ш/Д). однако транзисторы М2а и М2d являются устройствами с единственным транзистором, тогда как каждый из транзисторов М2b и М2с состоит из трех параллельных устройств того же самого размера, что и транзисторы М2а и М2d. Это показано на схеме на Фиг.5 обозначением m=3, относящимся к транзисторам М2b и М2с.

Транзистор М2а генерирует ток, представленный первым слагаемым, показанным в фигурных скобках уравнения (6с). То есть транзистор М2а генерирует ток, равный ID (VGS+3 VGS/2). Транзистор М2b генерирует третий ток, показанный в фигурных скобках уравнения (6с). То есть транзистор М2b генерирует ток, равный 3ID (VGS+ VGS/2). Транзистор М2b генерирует третий ток, показанный в фигурных скобках уравнения (6с). То есть транзистор М2b генерирует ток, равный 3ID (VGS+ VGS/2). Транзистор М2с генерирует второй ток, показанный в фигурных скобках уравнения (6с). То есть транзистор М2с генерирует ток, равный 3ID (VGS– VGS/2). Транзистор М2с генерирует второй ток, показанный в фигурных скобках уравнения (6с). То есть транзистор М2с генерирует ток, равный 3ID (VGS– VGS/2). Наконец, транзистор М2d генерирует четвертый ток, показанный в фигурных скобках уравнения (6с). То есть транзистор М2d генерирует ток, равный ID (VGS-3 VGS/2). Наконец, транзистор М2d генерирует четвертый ток, показанный в фигурных скобках уравнения (6с). То есть транзистор М2d генерирует ток, равный ID (VGS-3 VGS/2). VGS/2).

Токи транзисторов М2а и М2с суммируются при соединении их стоков вместе. Токи транзисторов М2b и М2d суммируются таким же образом.

Общие стоки транзисторов М2а, М2с и транзисторов М2b, М2d получают смещение через токовое зеркало, включающее в себя транзисторы М3а и М3b, причем транзисторы М3а и М3b являются МОП-транзисторами одинакового размера с каналом р-типа. Дифференциальное напряжение постоянного тока между стоками транзисторов М3а и М3b является сигналом постоянного тока, пропорциональным членам математического уравнения в фигурных скобках уравнения (6с) и, таким образом, пропорциональным коэффициенту разложения g3 3-го порядка. Если дифференциальное напряжение равно нулю, просуммированные токи через транзисторы М2а, М2с и М2b, М2d будут равными, а член математического выражения в фигурных скобках уравнения (6с) будет равен нулю.

Этот баланс токов обеспечивается операционным усилителем ОУ1 на Фиг.5, который работает аналогично операционному усилителю ОУ1 на Фиг.4. Более конкретно, операционный усилитель ОУ1 на Фиг.5 считывает дифференциальное напряжение постоянного тока между стоками транзисторов М3а и М3b и генерирует входное напряжение для резисторной цепочки 2R,R,R,2R, создающей цепь обратной связи. Эта цепь обратной связи автоматически поддерживает напряжение VGS, поданное на затвор М1 по Фиг.1а, на уровне, который обусловливает равенство нулю нелинейности 3-го порядка даже при наличии производственных и температурных отклонений.

Таким образом, настоящее изобретение обеспечивает возможность простого подхода к решению проблемы значительного снижения нелинейности или 2-го порядка, или 3-го порядка и демонстрирует низкую чувствительность к отклонениям в процессах, используемых при изготовлении транзисторов, и к температурным отклонениям. Хотя приведенные в качестве примера схемы смещения по Фиг.4 и Фиг.5 содержат дополнительные цепи, рост постоянного тока, требуемого для работы схем смещения по настоящему изобретению, является незначительным. Это является существенным преимуществом в применениях с батарейным питанием. Более того, токи смещения настоящего изобретения не ухудшают рабочие характеристики других схем, например уровень шума транзистора М1 (см. Фиг.1А). Более того, схемы смещения постоянного тока настоящего изобретения могут быть использованы для транзисторов (например, транзистор М1 на Фиг.1А), работающих фактически на любой частоте.

Описанные схемы смещения являются возможными вариантами осуществления изобретения. Имеются другие топологии схем смещения, которые могут генерировать оптимальные напряжения смещения, основанные на сведении к нулю напряжения постоянного тока или тока, пропорционального коэффициенту разложения 2-го или 3-го порядка. Изобретение может быть использовано в усилительных каскадах полевого МОП-транзистора, полевого транзистора с барьером Шотки (ПТБШ), транзистора с высокой подвижностью электронов (ТВПЭ), биполярного плоскостного транзистора (БПТ) и биполярного гетеротранзистора (БГТ), работающих на любой частоте.

Следует понять, что хотя различные варианты осуществления и преимущества настоящего изобретения были раскрыты в вышеприведенном описании, последнее является лишь иллюстративным, так что возможны изменения в деталях, не выходящие за пределы широких принципов изобретения. Поэтому настоящее изобретение должно ограничиваться лишь прилагаемой формулой изобретения.

Формула изобретения

1. Способ смещения транзистора, заключающийся в том, что генерируют сигнал постоянного тока (ПТ), пропорциональный выбранной нелинейности, и используют сигнал постоянного тока для генерирования напряжения смещения транзистора, при котором выбранная нелинейность равна нулю, отличающийся тем, что предусматривают схему обратной связи для считывания сигнала ПТ и автоматически регулируют напряжение смещения.

2. Способ по п.1, отличающийся тем, что выбранная нелинейность является нелинейностью второго порядка, а сигнал ПТ содержит первую, вторую и третью части.

3. Способ по п.2, отличающийся тем, что первую, вторую и третью части объединяют для формирования сигнала ПТ.

4. Способ по п.1, отличающийся тем, что выбранная нелинейность является нелинейностью третьего порядка, а сигнал ПТ содержит первую, вторую, третью и четвертую части.

5. Способ по п.4, отличающийся тем, что первую, вторую, третью и четвертую части объединяют для формирования сигнала ПТ.

6. Способ по п.1, отличающийся тем, что дополнительно предусматривают токовое зеркало для смещения элементов схемы, генерирующих сигнал ПТ.

7. Способ по п.1, отличающийся тем, что сигнал ПТ является односторонним или дифференциальным током.

8. Способ по п.1, отличающийся тем, что сигнал ПТ является односторонним или дифференциальным напряжением.

9. Транзисторная схема смещения, отличающаяся тем, что содержит множество транзисторов смещения, каждый из которых генерирует постоянный ток (ПТ), являющийся частью сигнала ПТ, пропорционального выбранной нелинейности, объединяющую схему, которая объединяет постоянные токи (ПТ) для формирования сигнала ПТ, и схему обратной связи для считывания сигнала ПТ и генерирования входного напряжения смещения транзисторов смещения, которое устраняет выбранную нелинейность.

10. Схема по п.9, отличающаяся тем, что выбранная нелинейность является нелинейностью второго порядка, характеризующейся первой, второй и третьей компонентами, причем множество транзисторов смещения включает в себя первый, второй и третий транзисторы смещения, генерирующие части сигнала ПТ, пропорциональные соответственно первой, второй и третьей компонентам.

11. Схема по п.10, отличающаяся тем, что объединяющая схема объединяет первую, вторую и третью части сигнала ПТ для формирования сигнала ПТ.

12. Схема по п.11, отличающаяся тем, что схема обратной связи выполнена с возможностью считывания сигнала ПТ и генерирования входного напряжения смещения транзисторов смещения, которое устраняет нелинейность второго порядка.

13. Схема по п.9, отличающаяся тем, что выбранная нелинейность является нелинейностью третьего порядка, характеризующейся первой, второй, третьей и четвертой компонентами, причем множество транзисторов смещения включает в себя первый, второй, третий и четвертый транзисторы смещения, генерирующие части сигнала ПТ, пропорциональные соответственно первой, второй, третьей и четвертой компонентам.

14. Схема по п.13, отличающаяся тем, что объединяющая схема объединяет первую, вторую, третью и четвертую части сигнала ПТ для формирования сигнала ПТ.

15. Схема п.14, отличающаяся тем, что схема обратной связи выполнена с возможностью считывания сигнала ПТ и генерирования входного напряжения смещения транзисторов смещения, которое устраняет нелинейность третьего порядка.

16. Схема по п.9, отличающаяся тем, что объединяющая схема включает токовое зеркало, связанное со множеством транзисторов смещения, для смещения множества транзисторов смещения.

17. Схема по п.9, отличающаяся тем, что схема обратной связи включает в себя операционный усилитель для считывания и усиления сигнала ПТ.

18. Схема по любому из пп.9-17, отличающаяся тем, что схема обратной связи включает в себя резисторную цепочку для генерирования отдельных напряжений смещения транзисторов смещения для обеспечения генерации ими частей сигнала ПТ.

19. Схема по п.9, отличающаяся тем, что сигнал ПТ является несимметричным или дифференциальным током.

20. Схема по п.9, отличающаяся тем, что сигнал ПТ является несимметричным или дифференциальным напряжением.

21. Схема смещения транзистора для минимизации искажения сигнала транзистора, содержащая средство смещения для генерирования сигнала постоянного тока (ПТ), пропорционального выбранной нелинейности, средство подачи сигнала ПТ для генерирования напряжения смещения транзистора, при котором выбранная нелинейность равна нулю, и схему обратной связи для считывания сигнала ПТ и для генерирования выходного напряжения смещения средства смещения, которое устраняет выбранную нелинейность.

22. Схема по п.21, отличающаяся тем, что выбранная нелинейность является нелинейностью второго порядка, а средство для генерирования сигнала ПТ генерирует первую, вторую и третью части.

23. Схема по п.22, отличающаяся тем, что первая, вторая и третья части объединяются для формирования сигнала ПТ.

24. Схема по п.21, отличающаяся тем, что выбранная нелинейность является нелинейностью третьего порядка, а средство для генерирования сигнала ПТ генерирует первую, вторую, третью и четвертую части.

25. Схема по п.24, отличающаяся тем, что первая, вторая, третья и четвертая части объединяются для формирования сигнала ПТ.

26. Схема по любому из пп.21-25, отличающаяся тем, что дополнительно содержит средство для образования токового зеркала для смещения средства для генерирования сигнала ПТ.

27. Схема по п.21, отличающаяся тем, что сигнал ПТ является несимметричным или дифференциальным током.

28. Схема по п.21, отличающаяся тем, что сигнал ПТ является несимметричным или дифференциальным напряжением.

РИСУНКИ

|

|